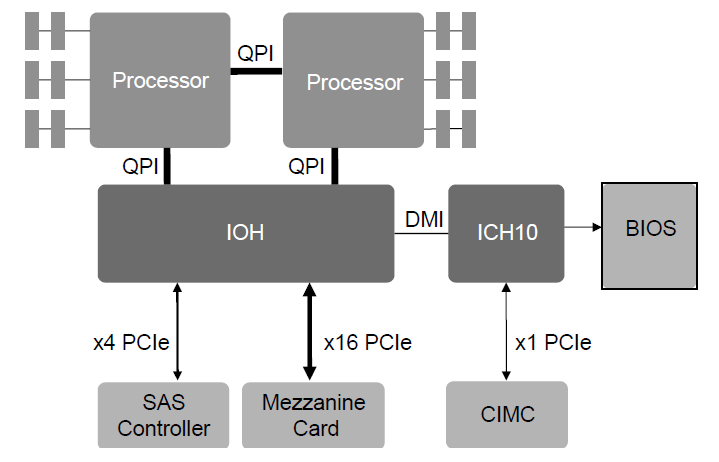

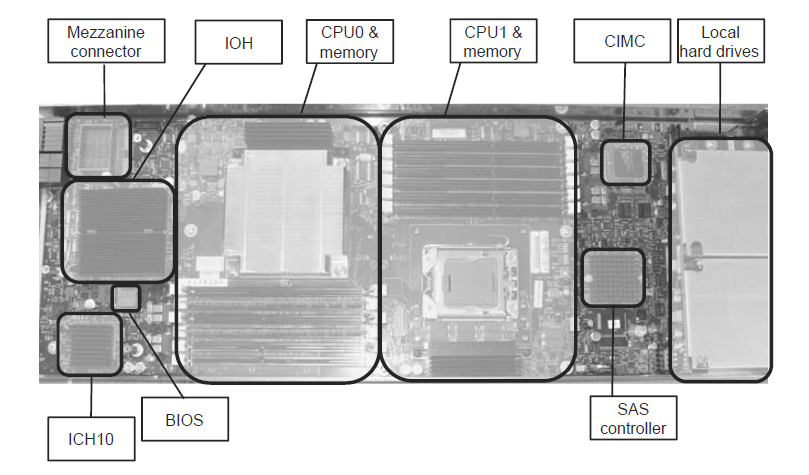

Two-Socket Blade Architecture

The two-socket UCS blades are based on Intel® reference architecture for dualsocket Nehalem-EP and Westmere-EP servers. These blades have multiple components in them. See figures below.

In computing, Direct Media Interface (DMI) is Intel’s proprietary link between the northbridge and southbridge on a computer motherboard. It was first used between the 9xx chipsets and the ICH6, released in 2004.

The Intel X58 (IOH) is an Intel chip designed to connect Intel processors with Intel QuickPath Interconnect (QPI) interface to peripheral devices. Supported processors implement the Nehalem microarchitecture and therefore have an integrated memory controller (IMC), so the X58 does not have a memory interface.

I/O Controller Hub (ICH) is a family of Intel southbridge microchips used to manage data communications between a CPU and a motherboard, specifically Intel chipsets based on the Intel Hub Architecture. It is designed to be paired with a second support chip known as a northbridge. As with any other southbridge, the ICH is used to connect and control peripheral devices (usb devices – mouse, keyboard, printer, etc)

The CPUs

The two-socket UCS blades use the Intel® Xeon® 5500/5600 series CPUs. Different CPU models can be installed on these blades. The Xeon 5500 CPUs (Nehalem-EP) have 4 cores and the Xeon 5600 (Westmere-EP) up to six cores. Hyper-Threading and TurboBoost capabilities are supported. Both type of CPUs are compliant with the Intel® Nehalem architecture.

The I/O Hub (IOH)

Both UCS blades use the Intel® X58 chip as an I/O Hub. This chip is connected to the CPUs with the Intel® QuickPath Interconnect (see “Intel® QuickPath Interconnect” in Chapter 2, page 31). The connectivity to the I/O Controller Hub is based on the Intel® Direct Media Interface (DMI). The Direct Media Interface is a point-to-point interconnection between the I/O Hub and the I/O Controller Hub.

The I/O Controller Hub

UCS Blades use the Intel® ICH10 I/O Controller Hub. This chip is sometimes referred to as “Southbridge” (old name). The ICH is used to connect various “lowspeed” peripherals, like USB devices, and it also provides connectivity for the Cisco Integrated Management Controller (CIMC), aka BMC (Board Management Controller), chip.

The Cisco Integrated Management Controler (CIMC)

In the UCS blades, the CIMC is used to provide pre-OS management access to blade servers and KVM (Keyboard Video and Mouse) access. It also functions as an aggregation point for the blade hardware. The CIMC used is a single chip, IP-based, server management solution. It provides the following functionality:

- General Inventory

- Blade Thermal, Power, and Health monitoring

- KVM access to blade

- Front panel video/USB access

- Serial over LAN

- Provide IPMI 2.0 interface to manage blade

The CIMC has two integrated 100Mb Ethernet connections that are connected in a redundant manner to the Chassis Management Switches inside the Fabric Extenders. The CIMC connects to the ICH10 via a PCIe connection. To provide the KVM function and the front panel video access, the CIMC has an integrated graphics engine.

The SAS Controller

The UCS blades use the LSI Logic 1064e storage processor. It supports 1.5 and 3GB/s SAS and SATA transfer rates. It has integrated mirroring and striping functions to provide different RAID availability levels for internal disks in blades.

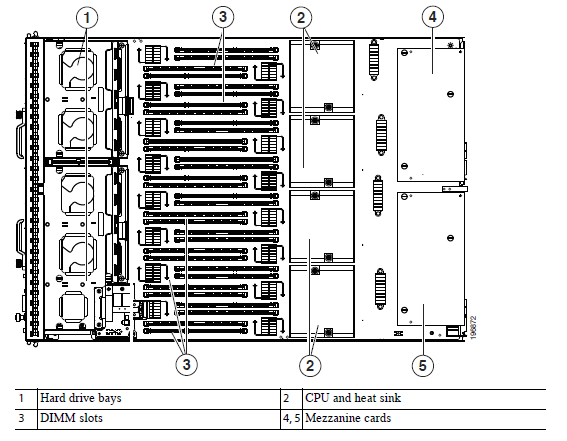

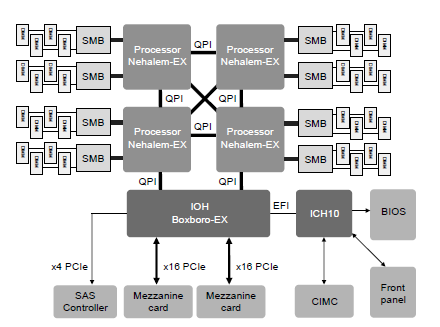

Four-Socket Blade Architecture

The four-socket UCS blades are based on Intel® reference architecture for four-socket Nehalem-EX servers.

The CPUs

The four-socket UCS blades use the Intel® Xeon® 7500 series CPUs. They have up to eight cores and Hyper-Threading and TurboBoost capabilities. The four sockets are fully interconnected with Intel’s QuickPath Interconnect (QPI) links. Two of the CPU sockets are also connected directly to the Boxboro IOH with QPI links. The remaining two CPU sockets access the IOH, through CPU-to-CPU QPI links. Attached to each CPU are four Mill Brook memory buffers (aka SMBs: Serial Memory Buffers), using Serial Memory Interface (SMI) links. Two DDR3 DIMM sockets per Mill Brook provide 32 DIMMs.

The I/O Hub (IOH)

The two main I/O paths toward the two mezzanine CNAs are provided through the Boxboro IOH PCIe ports. Two 16x PCIe Gen2 ports from the IOH support two PCIe mezzanine card options. These cards provide dual-ported 10Gbase-KR Ethernet links to the two UCS 2104XP fabric extenders. An embedded 6G SAS RAID controller is connected to the IOH through a 4x PCIe Gen2 port. This controller connects to the four disks on the board.

The I/O Controller Hub (IOC)

The ICH10R provides connections to the Cisco Integrated Management Controller (CIMC), aka BMC (Board Management Controller), the card Front-Panel, and an optional embedded USB module.

The Cisco Integrated Management Controller (CIMC)

Same as in Two-socket blade architecture